# N32H7xx Series Errata Sheet

# **Table of Contents**

| 1 List of Errata                                             | 3            |

|--------------------------------------------------------------|--------------|

| 1.1 Digital Filter Cannot Be Enabled When Reading GPIO I/J/K | Registers3   |

| 2 PWR                                                        | 3            |

| 2.1 Debugger Connection Issue in Sleep Mode                  | 3            |

| 3 AHB Cache                                                  | 4            |

| 3.1 Enabling AHB Cache Causes Legitimate Access to Be Blocke | ed4          |

| 4 RTC                                                        | 5            |

| 4.1 RTC Calibration Invalid                                  | 5            |

| 2 GPIO and AFIO                                              | 6            |

| 2.1 Digital Filter Cannot Be Enabled When Reading GPIO I/J/K | Registers6   |

| 3 PWR                                                        |              |

| 3.1 Debugger Connection Issue in Sleep Mode                  | 6            |

| 4 AHB Cache                                                  |              |

| 4.1 Enabling AHB Cache Causes Legitimate Access to Be Blocke | ed6          |

| 5 RTC                                                        | 7            |

| 5.1 RTC Calibration Invalid                                  | 7            |

| 6 TIMER                                                      | 7            |

| 6.1 Issue with Switching to 0% Duty Cycle PWM Mode in Force  | Active Mode7 |

| 7 I2C                                                        |              |

| 8 Chip Marking and Version Information                       |              |

| 9 Version History                                            | 10           |

| 10 Disclaimer                                                |              |

# 1 List of Errata

|                                                                         |                                               |   | Chip Revision |   |   |  |  |

|-------------------------------------------------------------------------|-----------------------------------------------|---|---------------|---|---|--|--|

|                                                                         | Errata Lit                                    | А | В             | С | D |  |  |

| GPIO and AFIO                                                           |                                               |   |               |   |   |  |  |

| 1.1 Digital Filter Cannot Be                                            |                                               |   |               |   |   |  |  |

| Enabled When Reading                                                    |                                               |   |               |   |   |  |  |

| GPIO I/J/K Registers                                                    |                                               |   |               |   |   |  |  |

| Description                                                             |                                               |   |               |   |   |  |  |

| The digital filter function cannot be                                   |                                               |   |               |   |   |  |  |

| enabled when reading GPIO I/J/K                                         |                                               |   |               |   |   |  |  |

| registers. Digital filters for other alternate functions work normally. |                                               |   |               |   |   |  |  |

| atternate functions work normany.                                       |                                               |   |               |   |   |  |  |

| Workaround                                                              | Digital Filter Cannot Be Enabled When Reading |   |               |   |   |  |  |

| None                                                                    | GPIO I/J/K Registers                          | • |               |   |   |  |  |

| None                                                                    |                                               |   |               |   |   |  |  |

| 2 PWR                                                                   |                                               |   |               |   |   |  |  |

|                                                                         |                                               |   |               |   |   |  |  |

| 2.1 Debugger Connection Issue in                                        |                                               |   |               |   |   |  |  |

| Sleep Mode                                                              |                                               |   |               |   |   |  |  |

| Description                                                             |                                               |   |               |   |   |  |  |

| After the chip enters sleep mode                                        |                                               |   |               |   |   |  |  |

| (SLEEP/STOP0/STOP2/STANDBY),                                            |                                               |   |               |   |   |  |  |

| the debugger cannot download or                                         |                                               |   |               |   |   |  |  |

#### **Table 1-1 Errata Overview**

# nsing.com.sg

| debug. The chip must exit sleep mode    |  |  |  |

|-----------------------------------------|--|--|--|

| first before using the debugger to      |  |  |  |

| download and debug.                     |  |  |  |

|                                         |  |  |  |

| Workaround                              |  |  |  |

|                                         |  |  |  |

| None                                    |  |  |  |

|                                         |  |  |  |

|                                         |  |  |  |

| 3 AHB Cache                             |  |  |  |

| 5 AID Cache                             |  |  |  |

|                                         |  |  |  |

| 3.1 Enabling AHB Cache Causes           |  |  |  |

|                                         |  |  |  |

| Legitimate Access to Be                 |  |  |  |

| Blocked                                 |  |  |  |

| вюскей                                  |  |  |  |

| Description                             |  |  |  |

|                                         |  |  |  |

| When CM4 enables AHB Cache,             |  |  |  |

| access permissions for all regions are  |  |  |  |

| forcibly changed to match the           |  |  |  |

| debugger's access permissions, which    |  |  |  |

| causes some legitimate accesses to be   |  |  |  |

| blocked, such as certain user APIs that |  |  |  |

| cannot be used.                         |  |  |  |

|                                         |  |  |  |

| Workaround                              |  |  |  |

| It is not recommended to enable AHB     |  |  |  |

| Cache when using CM4. It is             |  |  |  |

| recommended to execute CM4              |  |  |  |

| programs in AHB SRAM, which is 0-       |  |  |  |

| wait access SRAM, therefore AHB         |  |  |  |

| Cache is not needed.                    |  |  |  |

|                                         |  |  |  |

| <ul> <li>4 RTC</li> <li>4.1 RTC Calibration Invalid</li> <li>Description</li> <li>The RTC calibration mode does not work.</li> <li>Workaround</li> </ul> |                                                                        |   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---|--|--|

| PWR                                                                                                                                                      | Debugger Connection Issue in Sleep Mode                                | • |  |  |

| AHB Cache                                                                                                                                                | Enabling AHB Cache Causes Legitimate Access to<br>Be Blocked           | ٠ |  |  |

| RTC                                                                                                                                                      | RTC Calibration Invalid                                                | • |  |  |

| TIMER                                                                                                                                                    | Issue with Switching to 0% Duty Cycle PWM Mode<br>in Force Active Mode | • |  |  |

|                                                                                                                                                          |                                                                        |   |  |  |

|                                                                                                                                                          |                                                                        |   |  |  |

|                                                                                                                                                          |                                                                        |   |  |  |

|                                                                                                                                                          |                                                                        |   |  |  |

•: Issue exists

-: Issue does not exist

### 2 GPIO and AFIO

#### 2.1 Digital Filter Cannot Be Enabled When Reading GPIO I/J/K Registers

#### Description

The digital filter function cannot be enabled when reading GPIO I/J/K registers. Digital filters for other alternate functions work normally.

#### Workaround

None

### 3 PWR

#### 3.1 Debugger Connection Issue in Sleep Mode

#### Description

After the chip enters sleep mode (SLEEP/STOP0/STOP2/STANDBY), the debugger cannot download or debug. The chip must exit sleep mode first before using the debugger to download and debug.

#### Workaround

None

### 4 AHB Cache

#### 4.1 Enabling AHB Cache Causes Legitimate Access to Be Blocked

#### Description

When CM4 enables AHB Cache, access permissions for all regions are forcibly changed to match the

debugger's access permissions, which causes some legitimate accesses to be blocked, such as certain user APIs that cannot be used.

Workaround

It is not recommended to enable AHB Cache when using CM4. It is recommended to execute CM4 programs in AHB SRAM, which is 0-wait access SRAM, therefore AHB Cache is not needed.

### 5 RTC

#### 5.1 RTC Calibration Invalid

#### Description

The RTC calibration mode does not work.

#### Workaround

It is recommended to use a precise clock source that does not require calibration, such as LSE.

### **6 TIMER**

#### 6.1 Issue with Switching to 0% Duty Cycle PWM Mode in Force Active Mode

#### Description

All ATIM/GTIM in force active mode (OC1MD[2:0]=101) cannot properly implement switching to PWM mode with 0% duty cycle.

#### Workaround

None

# 7 I2C

#### **Timeout Counter Reset in Debug Mode**

#### Description

When in debug mode and the core is stopped, SMBus timeout can be set to stop or continue normal operation via DBG\_M7/M4APB1FZ.I2CxSTOP. However, the timeout counter will be reset, causing incorrect timeout values during debugging.

#### Workaround

None

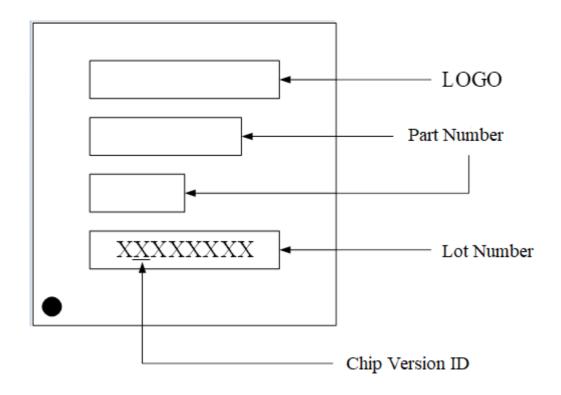

# 8 Chip Marking and Version Information

# 9 Version History

| Version | Date      | Changes       |

|---------|-----------|---------------|

| V1.0.0  | 2025.4.24 | First release |

|         |           |               |

### **10 Disclaimer**

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to Nations Technologies Inc. and Nations Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections. enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NATIONS has attempted to provide accurate and reliable information, NATIONS assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NATIONS be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product. NATIONS Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NATIONS and hold NATIONS harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NATIONS, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.

11 / 11