nsing.com.sg

**NSING**

**User Guide**

How to use the LSE clock security system to improve clock system

robustness

Introduction

The purpose of this document is to help users understand the security monitoring

function of LSE clocks, improve the robustness of the clock system, improve solution

security performance, and reducing the development time and complexity.

This document is only applicable to NSING MCU products. Currently, the supported

product include N32L43x, N32L40x, and N32G43x series.

## **Content**

| 1 | Introduction1                                |                                               |        |  |  |  |

|---|----------------------------------------------|-----------------------------------------------|--------|--|--|--|

|   | 1.1                                          | Overview                                      | 1      |  |  |  |

|   | 1.2                                          | Introduction to LSE Clocks                    | 1      |  |  |  |

|   | 1.3                                          | Introduction to LSI Clocks                    |        |  |  |  |

|   | 1.4                                          | Introduction to LSE Clock Security System (LS | ECSS)1 |  |  |  |

|   | 1.5                                          | Applicability                                 | 1      |  |  |  |

| 2 | Hard                                         | ware Environment                              | 2      |  |  |  |

|   | 2.1                                          | Demo Function                                 |        |  |  |  |

|   | 2.2                                          | Hardware Platform                             | 3      |  |  |  |

| 3 | Demo                                         | o Explain                                     | 4      |  |  |  |

|   | 3.1                                          | Demo Process                                  | 4      |  |  |  |

|   | 3.2                                          | Demo Analyze                                  | 5      |  |  |  |

|   | 3                                            | .2.1 USART1 Log Serial Port Initialization    | 5      |  |  |  |

|   | 3                                            | .2.2 Enable LSE                               | 6      |  |  |  |

|   | 3                                            | .2.3 Enable LSI                               |        |  |  |  |

|   | _                                            |                                               | 8      |  |  |  |

|   | 3                                            | Enter STOP2                                   |        |  |  |  |

|   | 3                                            | .2.6 Initialize LPTIM and LPUART              |        |  |  |  |

| 4 | User                                         | Guide                                         | 11     |  |  |  |

|   | 4.1                                          | Reset MCU                                     | 11     |  |  |  |

|   | 4.2                                          | Generate LSE Fault                            |        |  |  |  |

|   | 4.3                                          | LPTIMER Switch Clock Source                   |        |  |  |  |

|   | 4.4                                          | MCU Wakes Up From STOP2                       |        |  |  |  |

|   | 4.5                                          | MCU Enter STOP2 Sleep Mode                    | 14     |  |  |  |

|   | 4.6                                          | MCU Periodically Woken Up                     |        |  |  |  |

|   | 4.7                                          | LSE Recover                                   |        |  |  |  |

|   | 4.8 LPTIMER Switches The Clock Source to LSE |                                               |        |  |  |  |

| 5 | Version History                              |                                               |        |  |  |  |

| 6 | 6 Disalaiman                                 |                                               |        |  |  |  |

nsing.com.sg

**N**SING

Introduction 1

1.1 **Overview**

In some application scenarios, LSE failures may occur. Here, a method is proposed to use LSE-CSS to monitor LSE

failures. When a failure occurs, the system clock can be switched from LSE to LSI, avoid the LSE failure causing

the system stop running.

1.2 **Introduction to LSE Clocks**

The LSE crystal is a 32.768KHz low-speed external crystal or ceramic resonator. It provides a low-power and accurate

clock source for real-time clocks or other timing functions. The LSE crystal is enabled and disabled by setting the LSEEN bit in the Low Power Domain Control Register (RCC LDCTRL). The LSERD in the Low Power Domain Control Register

(RCC LDCTRL) indicates whether the LSE crystal oscillator is stable. During the startup phase, the LSE clock signal is

not released until this bit is set by hardware. If enabled in the clock interrupt register (RCC CLKINT), an interrupt request

can be generated.

1.3 **Introduction to LSI Clocks**

The LSI RC can provide clocks for IWDG and AWU in the STOP2 and STANDBY mode. The LSI clock frequency is

about 40KHz. The LSI RC can be enabled or disabled by the LSIEN bit in the Control/Status register (RCC CTRLSTS).

The LSIRD bit in the Control/Status register (RCC CTRLSTS) indicates whether the low-speed internal oscillator is stable.

During the startup phase, the clock is not released until this bit is set by hardware. If enabled in the clock interrupt register

(RCC\_CLKINT), an LSI interrupt request can be generated.

1.4 **Introduction to LSE Clock Security System (LSECSS)**

The LSE clock security system is activated by enabling the LSECLKSSEN bit in the Low Power Domain Control Register

(RCC LDCTRL). The LSECLKSSEN bit can be cleared by a hardware reset or RTC software reset or after detection of

an LSE fault. When the LSE and LSI are enabled and ready, the LSECLKSSEN bit must be enabled after configuring the

RTCSEL to select the RTC clock source. If an LSE failure is detected, LSE will no longer be provided to the RTC, but

the RTCSEL bits will not be modified by hardware to switch the RTC clock source. In STANDBY mode, an LSE clock

failure will trigger a wakeup. In other modes, an interrupt can be generated to wakeup, and then software can clear the

LSECLKSSEN bit and turn off the LSE, and changing the clock source of the RTC, and other measures to ensure

application security. The frequency of the LSE oscillator must be higher than 30KHz to prevent LSECSS false detection.

1.5 **Applicability**

This Demo is only applicable to N32L43x, N32L40x, N32G43x series MCU, supports KEIL5 platform.

[SDK-VER 1.1.0]

Release Date: 2021-11-30

1/18

## 2 Hardware Environment

#### 2.1 Demo Function

This demo mainly shows the developer how to switch the peripheral clock source to the LSI when the LSE fails, the system monitors the LSE clock, waits for the LSE to recover, and then switches the peripheral clock source from the LSI to the LSE.

#### 2.2 **Hardware Platform**

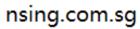

Figure 2-1 Hardware Platform

**Table 2-1 Hardware List**

| No. | Resource                  | Illustrate                         | Remark |

|-----|---------------------------|------------------------------------|--------|

| 1   | NS3602_SOCKET_LQFP48_V1.0 | Nations LQFP48 package test socket |        |

Email: sales@nsing.com.sg

| 2 | N32G435CBL7 | MCU |  |

|---|-------------|-----|--|

|---|-------------|-----|--|

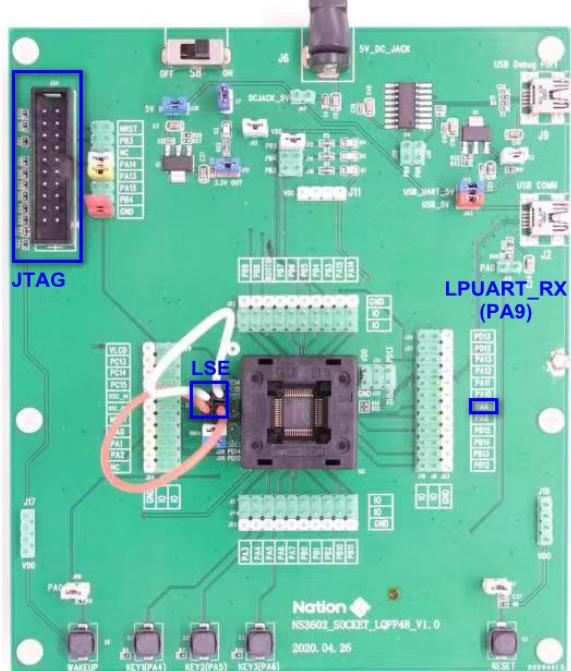

# Demo Explain

#### 3.1 **Demo Process**

Figure 3-1 Demo Flowchart

Email: sales@nsing.com.sg

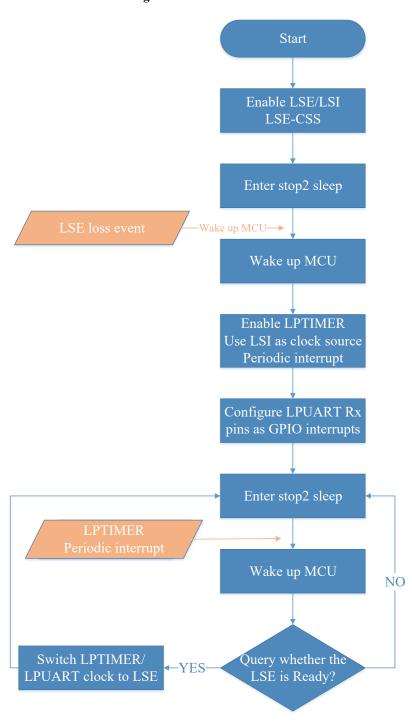

### 3.2 Demo Analyze

### 3.2.1 USART1 Log Serial Port Initialization

Figure 3-2 USART1 Serial Port Initialiaztion

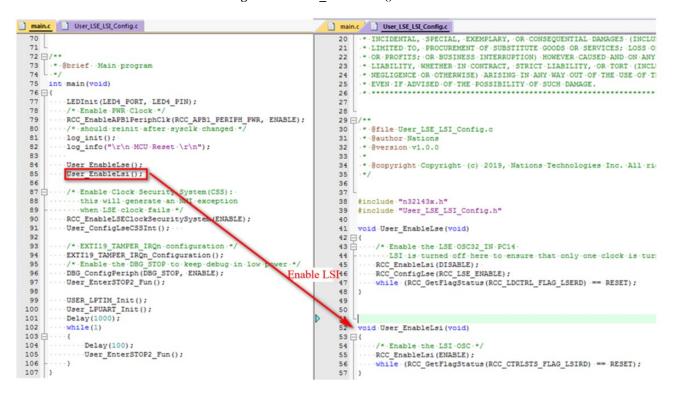

#### 3.2.2 Enable LSE

Figure 3-3 User EnableLse() Function

```

main.c User_LSE_LSI_Config.c

71 L

72 日/**

* DISCLAIMED. IN NO EVENT SHALL NATIONS BE LIABLE FOR ANY DIRECT

- DISCLAIMED. IN NO EVENT SHALL NATIONS BE LIABLE FOR ANY DIRECT INCIDENTAL, SPECIAL EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCL LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSSON OR PROFITS: OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON AN LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INC. MEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF SEVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

73 ** @brief · Main · program

74 **/

75 int ·main(void)

76 - (

LEDInit(LED4_PORT, LED4_PIN);

-/*:Enable PWR:Clock:*/

-RCC_EnableAPB1PeriphClk(RCC_APB1_PERIPH_PWR, ENABLE);

26

27

28

29 🗐 /

80

/* should reinit after sysclk changed .*

log_init();

log_info("\r\n MCU Reset \r\n");

81

82

83

84

85

86

. * . @file . User_LSE_LSI_Config.c

30

31

32

33

.* . @author . Nations

.* . @version . v1.0.0

User_EnableLse();

User_EnableLsi();

34

35

36

* · @copyright · Copyright · (c) · 2019, · Nations · Technologies · Inc. · All · r

Enable LSE

88

89

90

91

92

93

94

95

96

97

98

99

100

38

#include "n32143x.h"

#include "User_LSE_LSI_Config.h"

User_ConfigLseCSSInt();

40

41

42

43

/* EXTI19 TAMPER IRQn configuration */

EXTI19_TAMPER_IRQn_Configuration();

/* Enable the DBG_STOP to keep debug in DBG_Configeriph(DBG_STOP, ENABLE);

User_EnterSTOP2_Fun();

void User EnableLse (void)

g · in · low · power · */

·/* Enable the LSE OSC32_IN PC14

LSI is turned off here to ensure that only one clock is tu

RCC_EnableLsi(DISABLE);

RCC_ConfigLse(RCC_LSE_ENABLE);

while (RCC_GetFlagStatus(RCC_LDCTRL_FLAG_LSERD) == RESET);

45

46

47

48

49

50

51

USER_LPTIM_Init();

User_LPUART_Init();

Delay(1000);

102

while (1)

Delay(100);

User_EnterSTOP2_Fun();

52 VC

53 = {

54

55

void User_EnableLsi(void)

105

RCC EnableLsi (ENABLE);

while (RCC_GetFlagStatus(RCC_CTRLSTS_FLAG_LSIRD) == RESET);

```

#### 3.2.3 Enable LSI

Figure 3-4 User EnableLsi() Function

#### 3.2.4 Enable LSE-CSS Monitor

Figure 3-5 RCC EnableLSEClockSecuritySystem() Function

```

main.c User_LSE_LSI_Config.c n3243x_rcc.c

71 = /**

73 | ** @brief · Main · program

74 | .*/

75 | int · main (void)

76 ⊟ {

77 | · ·

78 | · ·

LEDInit (LED4_PORT, LED4_PIN);

/* · Enable · PWR · Clock · */

RCC_EnableAPB1PeriphClk(RCC_APB1_PERIPH_PWR, ENABLE);

80

/*.should.reinit.after.sysclk.changed.*/

-\log_{\texttt{info}("\r\n\cdot \texttt{MCU}\cdot \texttt{Reset}\cdot \r\n");}

82

Initialize LSE-CSS and

enable LSE-CSS interrupts

User_EnableLse();

User_EnableLsi();

84

85

86

Enable Clock Security System(CSS):

this will generate an NMI exception

when LSE clock fails **/

87

88

89

** @brief · Enables · or · disables · the · LSE · Clock · Security · System. .

* @param · Cmd · new · state · of · the · LSE · Clock · Security · System. .

* · · · This · parameter · can · be: · ENABLE · or · DISABLE.

1614

1615

90

91

RCC_EnableLSEClockSecuritySystem(ENABLE);

User_ConfigLseCSSInt();

/* EXTI19_TAMPER_IRQn configuration */

EXTI19_TAMPER_IRQn_Configuration();

1616

92

93

94

95

96

97

98

99

void RCC_EnableLSEClockSecuritySystem(FunctionalState Cmd)

1618

/*·Enable·the·DBG_STOP·to·keep·debug·in·low·power

·/*·Check·the·parameters·*/

DBG_ConfigPeriph(DBG_STOP, ENABLE);

User_EnterSTOP2_Fun();

1620

1621

1622

1623 }

USER_LPTIM_Init();

User_LPUART_Init();

Delay(1000);

100

void User_ConfigLseCSSInt(void)

62 ⊟ {

63 |

102

while (1)

RCC->CLKINT · · | = · (1 · << · 25);

103

Delay(100);

104

105

-User_EnterSTOP2_Fun();

106

```

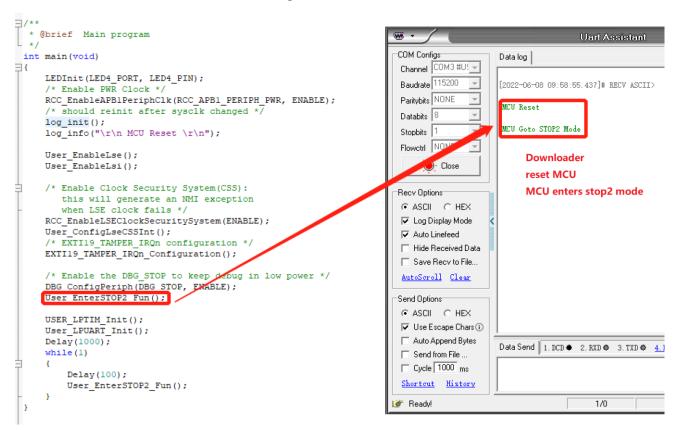

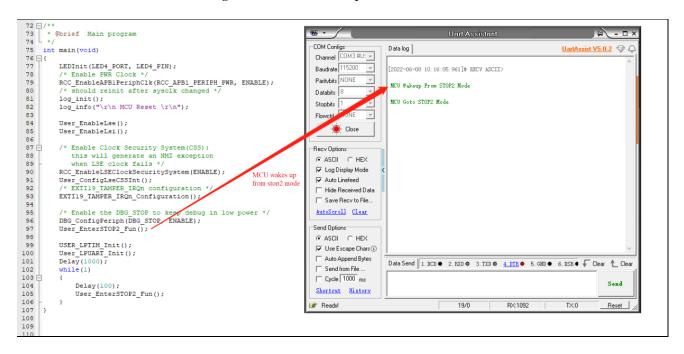

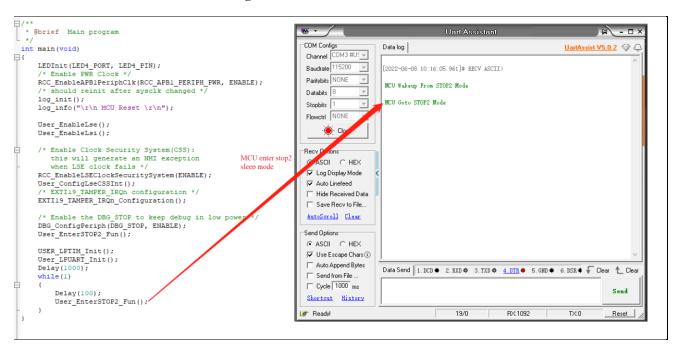

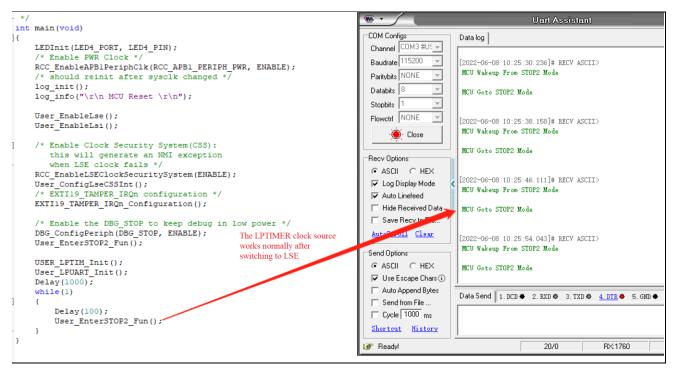

#### 3.2.5 Enter STOP2

Figure 3-6 User EnterSTOP2 Fun() Function

```

/* Request to enter STOP2 mode*/

65

PWR EnterSTOPZMode (PWR STOPENTRY WFI, PWR CTRL3 RAM1RET);

log_info("\n MCU-Wakeup·From·STOP2·Mode·\n");

66

67

68

69

70

71 - /**

73 74 75 ir 76 🖂 (

* · @brief · · Main · program

LEDInit (LED4_PORT, LED4_PIN);

78

79

-/* Enable PWR Clock */

-RCC_EnableAPB1PeriphClk(RCC_APB1_PERIPH_PWR, ENABLE);

80

/* should reinit after sysclk changed *

log_init();

log_info("\r\n.MCU-Reset.\r\n");

81

82

83

84

User_EnableLse();

85

User_EnableLsi();

86

·/*·Enable·Clock·Security·System(CSS):

....this will generate an NMI exception ....when LSE clock fails */

88

89

RCC_EnableLSEClockSecuritySystem(ENABLE);

90

91

User_ConfigLseCSSInt();

/* EXTI19 TAMPER_IRQn configuration */

EXTI19_TAMPER_IRQn_Configuration();

92

93

-/* Enable the DBG_STOP to keep debug in low power */

DBG_ConfigPeriph(DBG_STOP, ENABLE);

95

96

Enter stop2 sleep mode

97

98

User_EnterSTOP2_Fun():

62 void User_EnterSTOP2_Fun(void)

USER_LPTIM_Init();

User_LPUART_Init();

99

63 ⊟ {

64

·log_info("\r\n·MCU·Goto·STOP2·Mode·\n");

101

Delay(1000);

65

66

/* Request to enter STOP2 mode*/

PWR EnterSTOP2Mode(PWR STOPENTRY WFI, PWR CTRL3 RAM1RET);

102

while (1)

103

67 68 }

log_info("\n.MCU.Wakeup.From.STOP2.Mode.\n");

104

105

Delay(100);

User_EnterSTOP2_Fun();

106

107

```

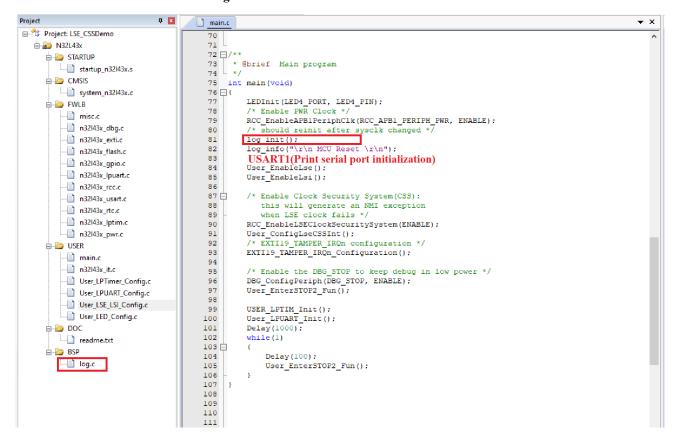

#### 3.2.6 Initialize LPTIM and LPUART

Figure 3-7 USER LPTIM Init() and User LPUART Init() Function

```

void User LPUART Init (void)

LPUART_InitType LPUART_InitStructure;

//* Configure the GPIO ports */

GPIO Configuration();

LEDInit(LED4_PORT, LED4_PIN);

73

74

75

76

77

78

79

80

81

82

/* Enable PWR Clock */

RCC_EnableAPB1PeriphClk(RCC_APB1_PERIPH_PWR, ENABLE);

//*-should-reinit-after-sysolk-changed-*/

····/*·System·Clocks·Configuration·*/

····RCC_Configuration(RCC_LPUARTCLK_SRC_LSE);

log_init();

log_info("\r\n·MCU·Reset·\r\n");

81

82

83

84

85

86

87

88

99

91

92

93

94

95

96

97

98

99

100

101

/* · LPUART · configuration · */

/* LPUART configuration */

LPUART_Delnit();

LPUART_Structure();

LPUART Structinit(&LPUART_InitStructure);

LPUART initStructure.BaudRate = 9600;

LPUART InitStructure.Parity = LPUART_PE_NO;

LPUART_InitStructure.RtsThreshold = LPUART_RTSTH_FIFOFU;

LPUART_InitStructure.Made = LPUART_MODE_RX | LPUART_MODE_TX;

/* Configure_LPUART */

LPUART_InitStructure.Mode = LPUART_MODE_RX | LPUART_MODE_TX;

/* Configure_LPUART_*/

User_EnableLse();

User_EnableLsi();

./*.Enable.Clock.Security.System(CSS):

....this.will.generate.an.NMI.exception

....when.LSE.clock.fails.*/

.RCC_EnableLSEClockSecuritySystem(ENABLE);

83

84

85

86

87

LPUART Init (&LPUART InitStructure);

User ConfigLseCSSInt(); -/* EXTI19 TAMPER IRQn configuration */

EXTI19 TAMPER IRQn Configuration();

void USER_LPTIM_Init(void)

/* Enable the DBG STOP to keep debug

68 = {

69 | 70 | 71 | 72 | 73 | 74 | 75 | 76 | 77 | 78 | 79 | 80 | 81 | }

DBG_ConfigPeriph(DBG_STOP, ENABLE):

User_EnterSTOP2_Fun();

-/* Enable interrupt · · */

LPTIMNVIC_Config(ENABLE);

RCC_ConfigLPTIMC1k(RCC_LPTIMC1k_SRC_LSE);

RCC_EnableRETPeriphC1k(RCC_RET_PERIPH_LPTIM,ENABLE);

Initialize

LPTIM/

LPUART

LPTIM_SetPrescaler(LPTIM,LPTIM_PRESCALER_DIV4);

LPTIM_EnableIT_CMPM(LPTIM);

/*-config-lptim-ARR-and-compare-register-*/

LPTIM_Enable(LPTIM);

102

103

104

105

while(1)

Delay(100);

User_EnterSTOP2_Fun();

LPTIM_SetAutoReload(LPTIM,65000);

LPTIM_SetCompare(LPTIM,60000);

LPTIM_StartCounter(LPTIM,LPTIM_OPERATING_MODE_CONTINUOUS);

```

#### 4 User Guide

#### 4.1 Reset MCU

Figure 4–1 Reset MCU

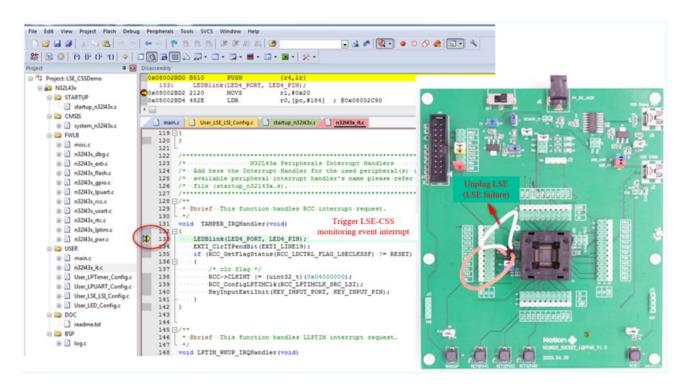

### **4.2** Generate LSE Fault

Figure 4-2 Generate LSE Fault

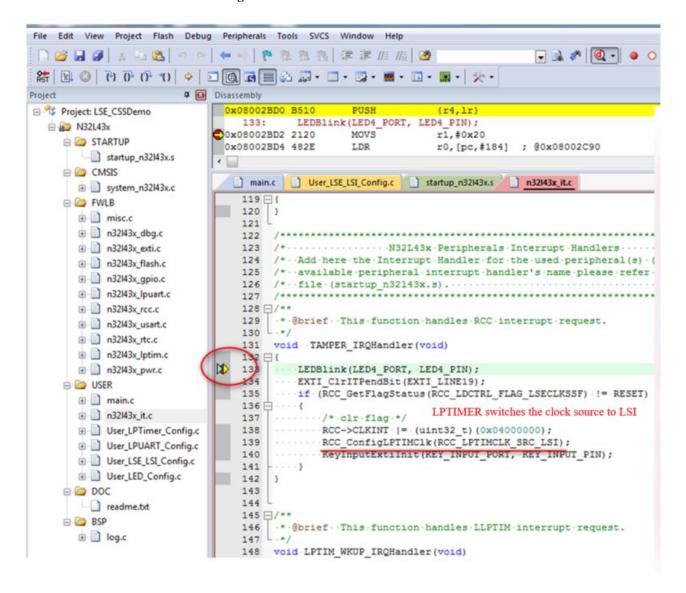

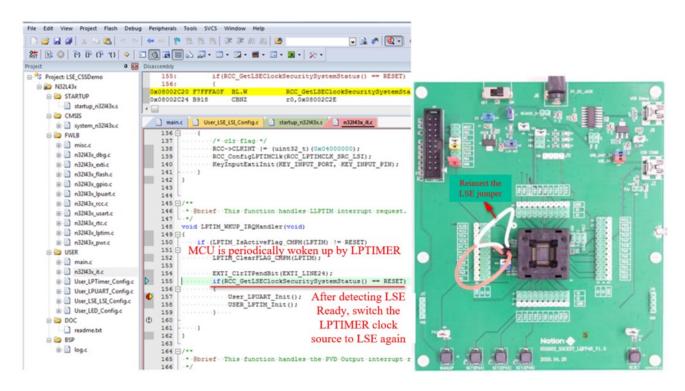

#### 4.3 LPTIMER Switch Clock Source

Figure 4-3 LPTIMER Switch Clock Source

### 4.4 MCU Wakes Up From STOP2

Figure 4-4 MCU Wake Up from STOP2 Mode

## 4.5 MCU Enter STOP2 Sleep Mode

Figure 4-5 MCU Enter STOP2 Mode

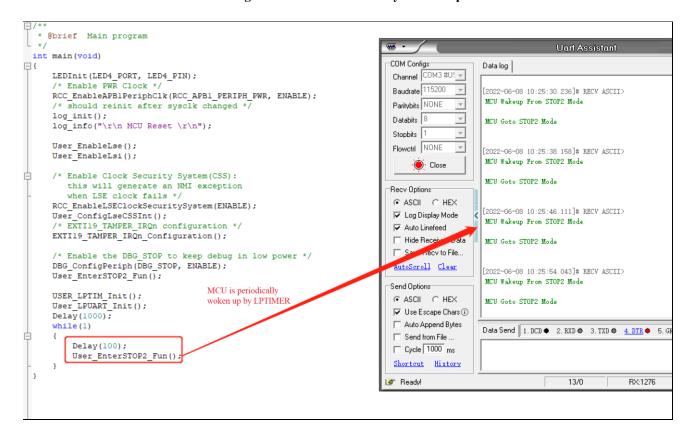

## 4.6 MCU Periodically Woken Up

Figure 4-6 MCU Periodically Woken Up

#### 4.7 LSE Recover

Figure 4-7 LSE Recover

#### 4.8 LPTIMER Switches The Clock Source to LSE

Figure 4–8 LPTIMER Switches the Clock Source to LSE

# 5 Version History

| Version | Date       | Changes         |

|---------|------------|-----------------|

| V1.0    | 2020.11.30 | Initial release |

|         |            |                 |

#### 6 Disclaimer

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to Nations Technologies Inc. and Nations Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections, enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NATIONS has attempted to provide accurate and reliable information, NATIONS assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NATIONS be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product. NATIONS Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NATIONS and hold NATIONS harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NATIONS, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.

18/18