# N32A455 Series Errata Sheet

NSING Technologies Pte. Ltd. Add: NSING, Teletech Park #02-28, 20 Science Park Road, Singapore 117674 Tel: +65 69268090 Email: sales@nsing.com.sg

| Contents |

|----------|

|----------|

| 1 Errata List                                                     | 4  |

|-------------------------------------------------------------------|----|

| 2 Power Control (PWR)                                             | 6  |

| 2.1 Stop2 Mode Wakeup                                             | 6  |

| 3 Reset And Clock Control (RCC)                                   | 7  |

| 3.1 System Timer (Systick)                                        |    |

| 4 GPIO and AFIO                                                   | 8  |

| 4.1 SPI1 Slave Mode, USART2 Sync Mode                             | 8  |

| 4.2 SPI1 Master Mode, USART2 Sync Mode                            |    |

| 4.3 SPI2 Slave Mode, USART3 Sync Mode                             |    |

| 4.4 SPI2 Master Mode, USART3 Sync Mode                            | 8  |

| 5 Analog/Digital Conversion (ADC)                                 | 10 |

| 5.1 ADC Data Left Alignment                                       | 10 |

| 5.2 ADC Analog Watchdog                                           | 10 |

| 5.3 ADC Injection Channel Triggers Regular Channel Conversion     | 10 |

| 5.4 Slave ADC Conversion Impacted By Master ADC Conversion        | 11 |

| 5.5 Affecting Adjacent ADC Data Registers                         | 11 |

| 6 Serial Peripheral Interface (SPI)                               | 12 |

| 6.1 SPI Interface                                                 | 12 |

| 6.1.1 SPI Baud Rate Setting                                       |    |

| 6.1.2 Checking Slave Mode CRC                                     | 12 |

| 6.2 I2S Interface                                                 | 13 |

| 6.2.1 PCM Long Frame Mode                                         | 13 |

| 7 I2C Interface                                                   | 14 |

| 7.1 Handling Software Events Before Current Byte Transferring     | 14 |

| 7.2 Notes On Single Read Of One Or Two Bytes                      | 14 |

| 7.3 Using DMA Simultaneously With Other Peripherals               | 15 |

| 7.4 The I2C Used As A Slave Device                                | 15 |

| 8 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 16 |

| 8.1 Parity Error Flag                                             | 16 |

| 8.2 RTS Hardware Flow Control                                     |    |

NSING Technologies Pte. Ltd. Add: NSING, Teletech Park #02-28, 20 Science Park Road, Singapore 117674 Tel: +65 69268090 Email: sales@nsing.com.sg

# **N**SING

# nsing.com.sg

| 9 Debug Interface (DBG)                  | 17 |

|------------------------------------------|----|

| 9.1 The Debug Registers                  | 17 |

| 10 Timer (TIM)                           | 18 |

| 10.1 Timer Repetitive Capture Detection  | 18 |

| 11 Real Time Clock (RTC)                 | 19 |

| 11.1 RTC Prescaler                       | 19 |

| 11.2 RTC Calibration                     | 19 |

| 11.3 RTC Timing                          | 19 |

| 11.4 RTC Periodic Wakeup                 | 19 |

| 11.5 RTC Digital Clock                   | 20 |

| 12 Chip Marking And Revision Description | 20 |

| 13 Version History                       | 21 |

| 14 Disclaimer                            | 22 |

# 1 Errata List

| Errata link                             |                                                                     |                                      |

|-----------------------------------------|---------------------------------------------------------------------|--------------------------------------|

| Ch 2: Power Control (PWR)               | 2.1: Stop2 mode wakeup                                              |                                      |

| Ch 3: Reset and Clock Control (RCC)     | 3.1: System Timer (Systick)                                         |                                      |

| Ch 4: GPIO and AFIO                     | 4.1: SPI1 slave mode, USART2 sync mode                              |                                      |

|                                         | 4.2: SPI1 master mode, USART2 sync mode                             |                                      |

|                                         | 4.3: SPI2 slave mode, USART                                         | 3 sync mode                          |

|                                         | 4.4: SPI2 master mode, USAR                                         | T3 sync mode                         |

| Ch 5: Analog/Digital Conversion (ADC)   | 5.1: ADC Data Left Alignment                                        |                                      |

|                                         | 5.2: ADC Analog Watchdog                                            |                                      |

|                                         | 5.3: ADC Injected Channel Trigger Regular Channel Conversion        |                                      |

|                                         | 5.4: Starting from ADC Conversion Affected by Master ADC Conversion |                                      |

|                                         | 5.5: Adjacent ADC Data Register Affected                            |                                      |

|                                         | 6.1: SPI interface                                                  | Section 6.1.1: SPI Baud Rate Setting |

| Ch 6: Serial Peripheral Interface (SPI) |                                                                     | Section 6.1.2: Slave Mode CRC check  |

|                                         | 6.2: I2S interface                                                  | Section 6.2.1: PCM Long Frame Mode   |

|                                         | 7.1: Software Events to be Man                                      | naged Before Current Byte Transfer   |

| Ch 7: I2C interface                     | 7.2: Considerations When Reading Single or Double Bytes once        |                                      |

|                                         | 7.3: Use DMA Simultaneously with Other Peripherals                  |                                      |

|                                         | 7.4: The I2C Used as a Slave I                                      | Device                               |

|                                         | 8.1: Parity Error Flag                                              |                                      |

#### Table 1-1 Overview Of Errata

4 / 22

NSING Technologies Pte. Ltd. Add: NSING, Teletech Park #02-28, 20 Science Park Road, Singapore 117674 Tel: +65 69268090 Email: sales@nsing.com.sg

| Ch 8: Universal Synchronous Asynchronous<br>Receiver (USART) | 8.2: RTS Hardware Flow Control       |

|--------------------------------------------------------------|--------------------------------------|

| Ch 9: Debug Interface (DBG)                                  | 9.1:Debug Register                   |

| Ch10: Timer (TIM)                                            | 10.1: Timer Repeat Capture Detection |

| Ch 11: Real Time Clock (RTC)                                 | 11.1: RTC Presale                    |

|                                                              | 11.2: RTC Calibration                |

|                                                              | 11.3: RTC Clock                      |

|                                                              | 11.4: RTC WakEup                     |

|                                                              | 11.5: RTC Digital Clock              |

# 2 Power Control (PWR)

### 2.1 Stop2 Mode Wakeup

### Description

When the MCU is in Stop2 mode, wakeup and NRST reset occurs simultaneously, the NRST reset cannot reset MCU.

Wakeup takes precedence, and the MCU will respond to the wakeup event first.

### Workaround

To resolve this issue, it is advised to avoid triggering an NRST reset of the MCU simultaneously with the wakeup event. Alternatively, if an NRST reset is necessary in a specific scenario, perform consecutive NRST resets to ensure the MCU is properly reset.

# **3** Reset And Clock Control (RCC)

# 3.1 System Timer (Systick)

### Description

The MCU can't be awakened when external clock source(STCLK) is chosen as clock source.

#### Workaround

To address this issue, configure the SysTick control register to use the core clock as the clock source instead of the External Reference Clock (STCLK).

# **4 GPIO and AFIO**

# 4.1 SPI1 Slave Mode, USART2 Sync Mode

### Description

With SPI1 and USART2 clocks already enabled, when pin PA4 is configured as a multiplexed output.SPI1 operating in slave mode with NSS software mode (SSMEN=1, SSEL=0), the USART2 clock in synchronous mode cannot be transmitted .

#### Workaround

No solution is provided for this issue.

## 4.2 SPI1 Master Mode, USART2 Sync Mode

### Description

With SPI1 and USART2 clocks already enabled, when pin PA4 is configured as a multiplexed output, SPI1 operating in master mode with NSS software mode (SSMEN=1, SSEL=0), the USART2 clock in synchronous mode cannot be transmitted .

### Workaround

Enable the SSOEN bit in SPI1 master mode.

### 4.3 SPI2 Slave Mode, USART3 Sync Mode

### Description

With SPI2 and USART3 clocks already enabled, when pin PB12 is configured as a multiplexed output, SPI2 operating in slave mode with NSS software mode (SSMEN=1, SSEL=0), the USART3 clock in synchronous mode cannot be transmitted.

### Workaround

No solution is provided for this issue.

# 4.4 SPI2 Master Mode, USART3 Sync Mode

### Description

8 / 22

With SP2 and USART3 clocks already enabled, when pin PB12 is configured as a multiplexed output, SPI2 operating in master mode with NSS software mode (SSMEN=1, SSEL=0), the USART3 clock in synchronous mode cannot be transmitted.

### Workaround

Enable the SSOEN bit in SPI2 master mode.

# 5 Analog/Digital Conversion (ADC)

# 5.1 ADC Data Left Alignment

### Description

In the ADC single conversion mode, when using a non-12bit precision with left alignment, and triggering the conversion of regular channels by software, the most significant bit of the invalid bits in the ADC\_DAT register is 1.

### Workaround

To address this issue, either retain only the valid data bits or switch to right-aligned mode.

# 5.2 ADC Analog Watchdog

### Description

In ADC independent mode, with single conversion, and non-12-bit precision, enabling the analogue watchdog feature, and triggering the conversion of regular/injected channels by software, if the high threshold value of the analogue watchdog has valid bits equal to the value in the ADC data register, with all invalid bits set to 0, it may lead to a false triggering of the analogue watchdog.

### Workaround

In this situation, ensure that the most significant bit of the invalid bits in the high threshold value of the analogue watchdog is set to 1 to prevent unintended triggering.

# 5.3 ADC Injection Channel Triggers Regular Channel Conversion

### Description

In continuous conversion mode, with external triggering disabled for regular channels and only software-triggered injection channel conversions, it is possible that the regular channels may be inadvertently triggered, leading to data being generated in the ADC\_DAT register, and the corresponding status bit in ADC\_STS for regular channel conversions being set.

### Workaround

Ignore the flags bits and data generated by regular channel conversions..

10 / 22

### 5.4 Slave ADC Conversion Impacted By Master ADC Conversion

### **Description:**

When the ADC operates in dual ADC mode and synchronous injected mode, and only the software triggers the regular channel conversion of the master ADC, the regular channels of the slave ADC are also triggered. Additionally, the lower 16 bits from the ADC\_DAT of the slave ADC are merged into the upper 16 bits of the master ADC\_DAT.

### Workaround:

No solution is provided for this issue.

## 5.5 Affecting Adjacent ADC Data Registers

### **Description:**

In independent mode, when software triggers the conversion of the ADC4/2 regular channels, the lower 16 bits of the ADC4/2 DAT register content are merged into the upper 16 bits of the ADC3/1 DAT register.

### Workaround:

No solution is provided for this issue.

# 6 Serial Peripheral Interface (SPI)

## 6.1 SPI Interface

### 6.1.1 SPI Baud Rate Setting

### Description

CRC validation may fail if SPI master mode, when setting the bitrate control bits (BR[2:0]) to fPLCK/2

### Workaround

Avoid setting the bitrate control bits (BR[2:0]) to fPLCK/2 in this scenario.

### 6.1.2 Checking Slave Mode CRC

### Description

In SPI operating in slave mode with CRC verification enabled, even if the NSS pin is at a high level, CRC calculation continues if the SPI receives a clock signal

### Workaround

Before using CRC validation , clear the CRC data register to ensure synchronization between the CRC checks of the master and slave devices

The clearing steps are as follows:

- 1. Reset the SPI enable bit (set to 0)

- 2. Reset the CRC validation bit (set to 0)

- 3. Set the CRC validation bit (set to 1)

- 4. Set the SPI enable bit (set to 1)

## 6.2 I2S Interface

### 6.2.1 PCM Long Frame Mode

### Description

When I2S is operating in master mode, PCM long frame mode, and the data format is directly set to 32-bit or is extended from 16-bit to 32-bit, the WS(word select) signal occurs every 16bits instead of every 32bits.

### Workaround

If I2S must operate in master mode and use long frame mode, it is recommended to use only the 16-bit data mode to ensure proper WS signal alignment.

# 7 I2C Interface

# 7.1 Handling Software Events Before Current Byte Transferring

### Description

In the occurrence of events EV7, EV7\_1, EV6\_1, EV6, EV2, EV8, and EV3, it is essential to handle the events before the current byte transfer to prevent issues such as reading an extra byte, obtaining duplicate data, or losing data. If the software fails to read the N-1 data before the stop signal generation, the data in the shift register for the Nth byte may become corrupted (shifted left by one bit).

### Workaround

- 1. When transferring more than one byte in I2C, consider using DMA if possible.

- 2. When using I2C interrupts, set the interrupt priority to the highest priority in the application

- 3. When the read data reaches the N-1 byte:

- a) Check that BSF(Byte Shift Flag) is set to 1

- b) Configure SCL as a GPIO open-drain output and set it to 0

- c) Set STOPGEN to 1

- d) Read the N-1 byte

- e) Configure SCL back to I2C multiplex open-drain output mode.

- f) Read the last byte

### 7.2 Notes On Single Read Of One Or Two Bytes

### Description

In master read mode, errors in reading data may occur when reading single-byte and doublebyte lengths.

### Workaround

- 1. Single byte Read:

- a) Upon receiving ADDRF

- b) Set ACKEN to 0

- c) Clear ADDRF bit (by reading STS1 first and then STS2)

- d) Set STOPGEN to 1

- e) Read one byte of data.

- 2. Double-byte Read:

- a) Upon receiving ADDRF

- b) Set ACKPOS to 1

- c) Clear ADDRF bit (by reading STS1 first and then STS2)

- d) Set ACKEN to 0

- e) Check that BSF (Byte Shift Flag) is 1

- f) Set STOPGEN to 1

- g) Read two consecutive bytes of data

# 7.3 Using DMA Simultaneously With Other Peripherals

### Description

During I2C communication using DMA, it may lead to abnormal I2C communication,

if there are other peripherals also use the same DMA controller.

### Workaround

- 1. Use different DMA controllers.

- 2. Disable DMA for other peripherals during I2C DMA communication.

# 7.4 The I2C Used As A Slave Device

### Description

When I2C is used as a slave device, an abnormal state occurs and cannot be recovered.

### Workaround

When I2C is used as a slave device, adding a timeout detection function to reset the I2C module when the timeout occurs.

# 8 Universal Synchronous Asynchronous Receiver Transmitter (USART)

### 8.1 Parity Error Flag

### Description

During the reception of a byte of data, if a parity error is detected before receiving the stop bit, the parity error flag is set. During this period, the parity error flag cannot be cleared through software (by reading the status register and then reading data register again). If the parity error interrupt is enabled, it may repeatedly enter the parity error interrupt handling function

#### Workaround

- 1. When the read data buffer flag is set and data is received, clear the parity error flag.

- 2. Disable the parity error interrupt during the first entry into the parity error interrupt, then re-enable it after receiving the data.

### 8.2 RTS Hardware Flow Control

#### Description

When the RTS(Request to Send) hardware flow control is enabled, and a USART receives a frame of data, the RTS signal is automatically asserted (pulled high) upon receiving the first byte of data. If this first byte is not promptly read from the data register, upon receiving the next byte of data, the RTS signal is de-asserted (pulled low) again, and the USART waits for the reception of the next frame of data.

#### Workaround

Read the data from the data register promptly before receiving the next new data.

# 9 Debug Interface (DBG)

## 9.1 The Debug Registers

### Description

The DBGMCU\_IDCODE debugging register can only be accessed in debug mode (not accessible to user programs). When attempting to read it in user mode, the returned value is 0xFF.

### Workaround

Avoid using IDCODE in user applications to prevent issues related to its restricted access in non-debug modes.

# 10 Timer (TIM)

## **10.1 Timer Repetitive Capture Detection**

### Description

When an input capture occurs, if a new input capture is generated during the reading of TIMx\_CCDATx (capture/compare register x) –where the read operation automatically clears the capture flag –the CCxOCF(capture/compare x repeated capture flag) might still remain set.

#### Workaround

No solution is provided for this issue.

# 11 Real Time Clock (RTC)

### 11.1 RTC Prescaler

### Description

The asynchronous prescaler factor and the synchronous prescaler factor in the RTC cannot be set to 0, as it may lead to RTC pre-allocation to failure.

### Workaround

Avoid setting the asynchronous prescaler register (TRC\_PRE) DIVA[6:0](asynchronous prescaler segment) and DIVS[14:0](synchronous prescaler segment) to 0.

## 11.2 RTC Calibration

### Description

During RTC automatic calibration (when the CP bit in the RTC\_CALIB register is set to 1), the automatic calibration may not successful if the asynchronous prescaler factor (DIVA) is not set to 128/64/32/16/8.

### Workaround

To ensure successful RTC automatic calibration, choose an asynchronous prescaler (DIVA) factor of 128/64/32/16/8.

# 11.3 RTC Timing

### Description

While the RTC is active, if an NRST (external reset) occurs, the reset period will cause the RTC

to stop counting.

### Workaround

No solution is provided for this issue.

# 11.4 RTC Periodic Wakeup

### Description

Periodic wake-up from the RTC module does not work to wake up from STANDBY mode.

19 / 22

### Workaround

Use the RTC alarm wake-up feature instead of the periodic wake-up.

# **11.5 RTC Digital Clock**

### Description

The RTC digital clock precision calibration function is not recommended.

### Workaround

No solution is provided for this issue.

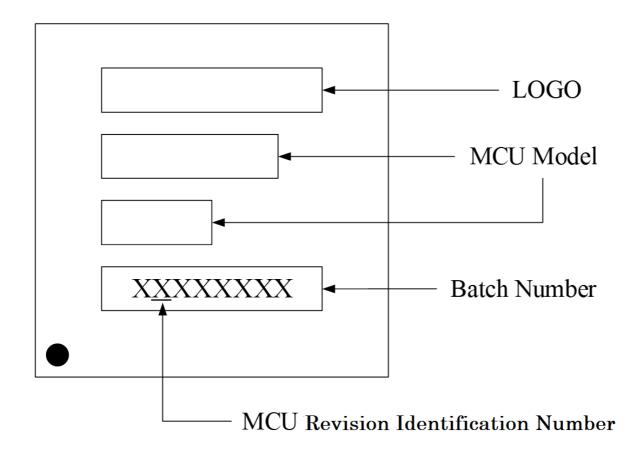

# **12 Chip Marking And Revision Description**

# **13 Version History**

| Version | Date       | Changes                                                                                                                                          |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.0.0  | 2022.06.20 | The initial release                                                                                                                              |

| V1.1.0  | 2023.06.28 | <ol> <li>Added RTC wake-up correction item</li> <li>Added I2C used as slave device correction item</li> <li>Added RTC correction item</li> </ol> |

|         |            |                                                                                                                                                  |

# nsing.com.sg

### 14 Disclaimer

This document is the exclusive property of NSING TECHNOLOGIES PTE. LTD. (Hereinafter referred to as NSING). This document, and the product of NSING described herein (Hereinafter referred to as the Product) are owned by NSING under the laws and treaties of Republic of Singapore and other applicable jurisdictions worldwide. The intellectual properties of the product belong to Nations Technologies Inc. and Nations Technologies Inc. does not grant any third party any license under its patents, copyrights, trademarks, or other intellectual property rights. Names and brands of third party may be mentioned or referred thereto (if any) for identification purposes only. NSING reserves the right to make changes, corrections. enhancements, modifications, and improvements to this document at any time without notice. Please contact NSING and obtain the latest version of this document before placing orders. Although NATIONS has attempted to provide accurate and reliable information, NATIONS assumes no responsibility for the accuracy and reliability of this document. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. In no event shall NATIONS be liable for any direct, indirect, incidental, special, exemplary, or consequential damages arising in any way out of the use of this document or the Product.

NATIONS Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, Insecure Usage'. Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, all types of safety devices, and other applications intended to supporter sustain life. All Insecure Usage shall be made at user's risk. User shall indemnify NATIONS and hold NATIONS harmless from and against all claims, costs, damages, and other liabilities, arising from or related to any customer's Insecure Usage Any express or implied warranty with regard to this document or the Product, including, but not limited to. The warranties of merchantability, fitness for a particular purpose and non-infringement are disclaimed to the fullest extent permitted by law. Unless otherwise explicitly permitted by NATIONS, anyone may not use, duplicate, modify, transcribe or otherwise distribute this document for any purposes, in whole or in part.